安心・安全な情報化社会の構築をめざして

※掲載内容は執筆当時のものです。

超高信頼性VLSI製造のための故障検査技術の開発

近年、コンピュータとネットワークによって構成された情報システムを基盤として、私たちの生活は飛躍的に快適になっています。一方で、情報システムを構成するコンピュータのハードウェアおよびソフトウェアの不具合が、一つの機器の不具合としておさまらず、社会生活に必要なサービスを中断する事態となって報道されることも多くなっています。最悪の場合は、コンピュータのハードウェアおよびソフトウェアの不具合によって人命や財産が失われるかもしれません。

近年、コンピュータとネットワークによって構成された情報システムを基盤として、私たちの生活は飛躍的に快適になっています。一方で、情報システムを構成するコンピュータのハードウェアおよびソフトウェアの不具合が、一つの機器の不具合としておさまらず、社会生活に必要なサービスを中断する事態となって報道されることも多くなっています。最悪の場合は、コンピュータのハードウェアおよびソフトウェアの不具合によって人命や財産が失われるかもしれません。

そこで、安心・安全な情報化社会の構築をめざして、コンピュータの信頼性を向上させるために、超高信頼化VLSI(ディペンダブルVLSI)の設計・製造・検査を行う技術を確立することは必要不可欠であり、それらの解決が急がれています。

我々の研究グループでは、微細加工された高機能・高速なVLSIを対象として、新しい故障モデルの提案、およびそれに基づく故障検査法を提案しています。

研究の特色

VLSIの故障は、VLSIを構成するトランジスタ内および配線における断線や短絡が主な原因です。故障検査は、故障検出のためのテストパターンを生成すること、および被検査回路の故障箇所を指摘する故障診断からなっています。

私達は病気を早期に発見するために人間ドックにおいて、さまざまな検査を受け、医師はその検査結果に従って患者の病気を診断します。尊い人命を救うためには、人間ドックの検査精度を向上させることが重要です。同様に、VLSIの信頼性を向上させるためには、製品として出荷する前に効率よく良品/不良品の判定を行い、不良品に対しては正確に故障位置および故障の原因を究明することが重要です。

最近、VLSIにおいては、その製造方法が微細化されています。最先端のVLSIにおける配線幅のサイズは65ナノメートル(1ナノメートル:10億分の1メートル)です。微細化に伴って、従来の故障検査法では対応できない事態が発生しています。そこで、私たちの研究グループは、配線の断線故障、短絡故障、微小な遅延故障に対する新しい故障モデルの提案およびその故障検査法の開発に関して研究を進めてきました。

研究の魅力

私達の研究成果は、現在のVLSIの製造に直接適用可能なものもあります。共同研究においては、産業界で使用されている商用テストEDAツールの性能に対して、私たちが開発したプロトタイプのテストEDAツールの性能が優位である場合もあります。その際には共同研究先の企業から感謝され、研究に参加してくれた学生とともに喜びをわかちあいます。また、共同研究に従事した学生が、産業界で活躍していることを聞くことも喜びのひとつです。

研究の展望

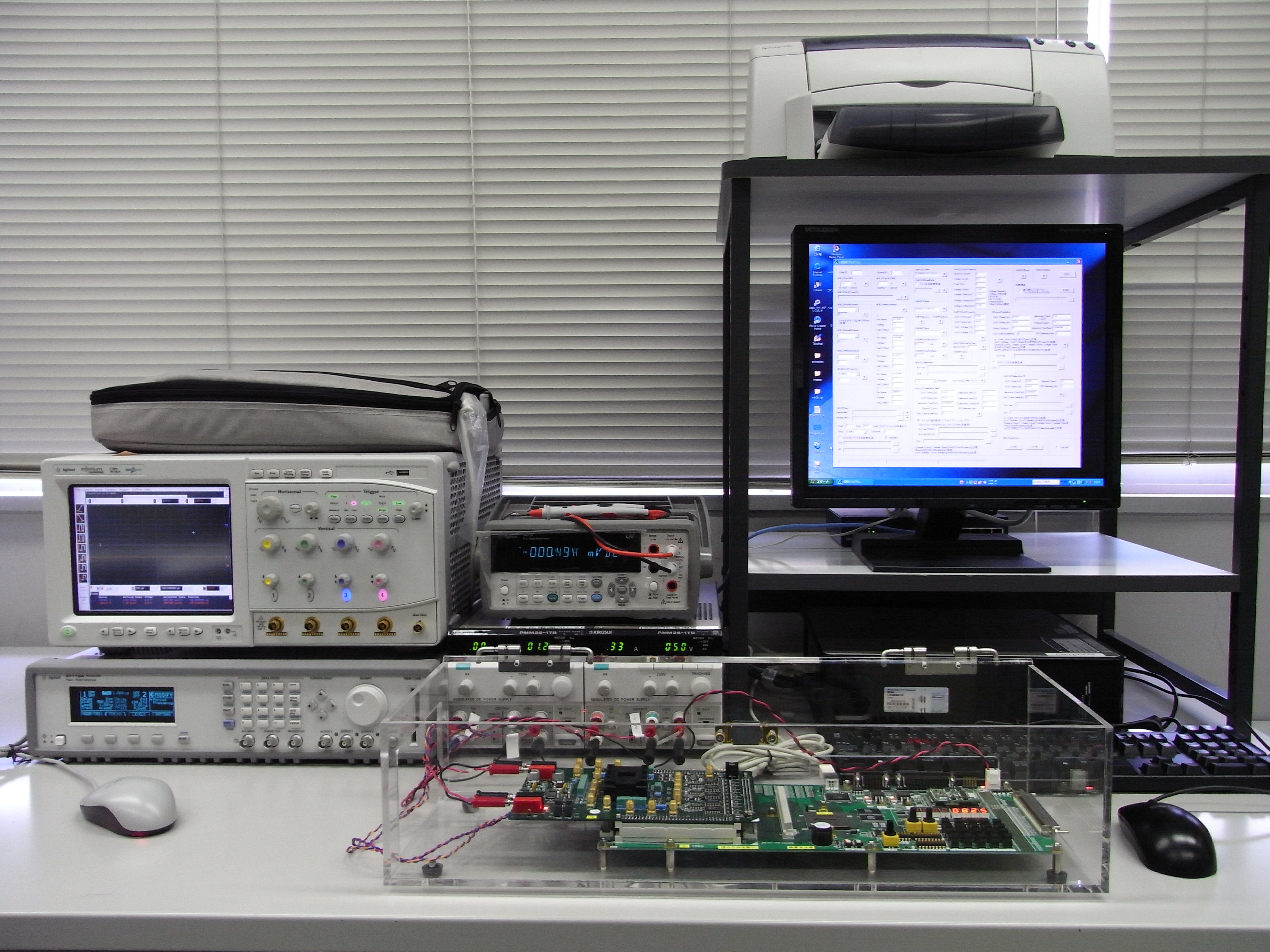

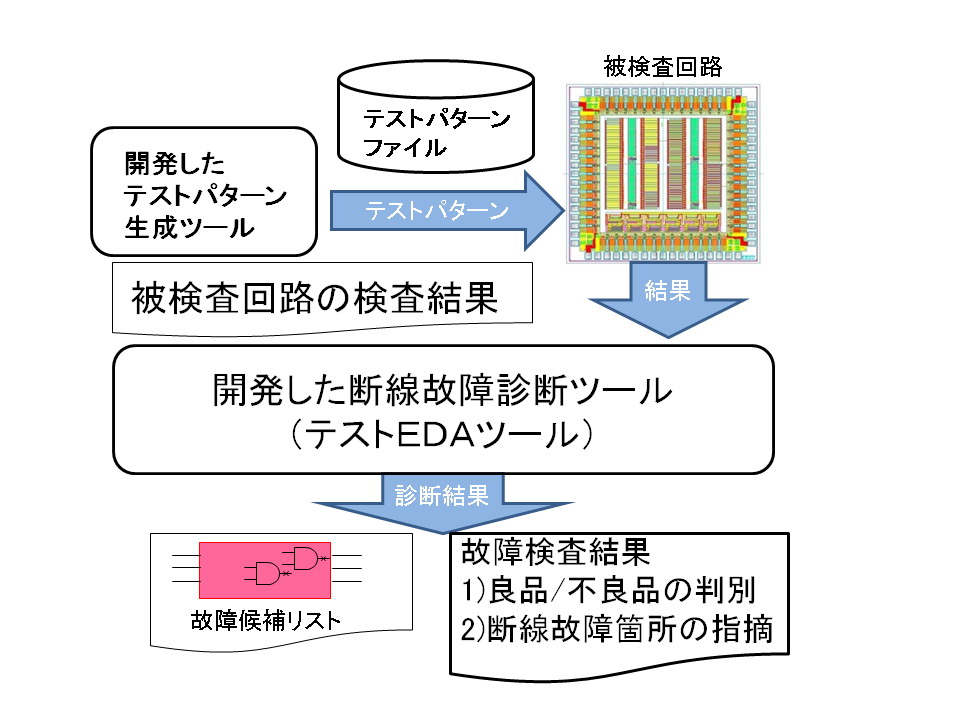

私たちの研究グループの最近のテーマは、微細化された配線の断線故障に対する新しい故障モデルの提案およびその故障検査法の開発です。配線の断線故障は、現在、欧米の大学・産業界も注目している国際競争的な研究テーマです、私達は、国内の複数の大手半導体企業が共同設立した株式会社半導体理工学研究センター(STARC)、徳島大学、および明治大学と共同で研究を進めています。新しい故障モデルを提案するために、私達の研究グループでは、コンピュータシミュレーション(電磁界シミュレータおよび電子回路シミュレータ)による断線故障の振る舞いの解析、意図的に断線故障を埋め込んだ最先端プロセスでのVLSIの試作、その試作VLSIの計測結果に基づく解析、および新しい故障モデルに基づく故障検査法を提案しています。このような統合的な研究手法は、独創性の高い研究手法として評価されています。写真は、私達の研究グループが90ナノプロセスで製作した断線故障検証用VLSIおよび共同開発した簡易LSIテスタシステムです。また、開発した断線故障用テストEDAツール(EDA: Electronic Design Automation)の概要を図に示しています。

- 簡易LSIテスタシステム

- テストEDAツール

この研究を志望する方へ

この研究では、物の仕組みに興味をもち、常に工夫をして、改良しようとする気持ちが必要です。研究成果を得るためには、非常に長い時間と多大な労力が必要です。日々は、失敗と悩みの連続です。長く足踏みの状態が続いても、1年後、3年後、5年後のなりたい自分を(求めている成果を)心に強く描いて、一緒に研究に取り組んでみませんか。あきらめないで、一歩ずつ前に進み続ければ、必ず道は成果へとつづきます。みなさんの成果が、未来を支えていくのです。